| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | |||

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 |

- 로봇 산업

- 주식 투자

- 인플레이션

- 주식 차트 분석

- 휴머노이드 로봇

- 가치 투자

- 주식투자

- 리가켐바이오

- 미래 기술

- 메모리 풀링

- 기술적 분석

- HBM

- LCB39

- 눌림목 매매

- 펀더멘탈

- AI 반도체

- 재테크

- 스마트 팩토리

- 신약 개발

- 분산 투자

- 인공지능

- 엑시콘

- 투자 심리

- 바이오 투자

- LCB84

- ADC

- 투자 전략

- CXL

- 로봇 기술

- CXL 3.0

- Today

- Total

월가의 제갈공명

반도체 제조 공정 본문

여러분, 우리가 매일 손에서 놓지 않는 스마트폰이나 노트북의 두뇌인 반도체가 사실은 평범한 '모래'에서 시작된다는 사실, 알고 계셨나요? 😊 정말 신기하지 않나요? 거친 모래가 어떻게 전 세계 산업을 움직이는 핵심 부품이 되는지, 그 신비로운 8단계의 여정을 저와 함께 차근차근 따라가 봐요!

1. 배어 웨이퍼(Bare Wafer) 제조 공정

반도체 웨이퍼(Wafer) 제조 공정: 원재료 → 단결정 → 슬라이스 → 표면 완성

1️⃣ 원재료 정제 (고순도 실리콘 확보)

- 출발 원료: 석영(Quartz, SiO₂)

- 정제 과정

- 석영 → 금속 실리콘(MG-Si, ~98%)

- 화학 정제(지멘스 공정 등) → 전자급 실리콘(EG-Si, 99.9999999% 이상)

- 목적: 불순물(ppb~ppt 수준) 제거 → 반도체 전기적 특성 확보

2️⃣ 단결정 잉곳 성장 (Crystal Growth)

- 대표 방식: CZ(Czochralski) 공정

- 절차

- 고순도 폴리실리콘 용융

- 씨드(seed) 결정 삽입

- 회전·인출 → 원자 배열이 완벽한 단결정 실리콘 잉곳 형성

- 도핑(Doping): 붕소(B), 인(P) 등 첨가 → p형 / n형 결정 제어

3️⃣ 잉곳 가공 (Ingot Shaping)

- 외형 가공

- 원통 연마(Grinding)

- 양끝 절단(Cropping)

- 결정 방향 표시

- Flat 또는 Notch 가공

- 이후 포토 공정 정렬 기준 역할

4️⃣ 웨이퍼 슬라이싱 (Wafer Slicing)

- 방식: 다이아몬드 와이어쏘(Wire Saw)

- 두께

- 300mm 웨이퍼 기준 약 0.7~0.8mm

- 특징

- 수백 장의 웨이퍼를 연속 절단

- 절단면 손상 발생 → 후공정 필요

5️⃣ 래핑 & 에칭 (Lapping / Etching)

- 래핑(Lapping)

- 양면 연마 → 두께 균일화

- 에칭(Etching)

- 화학 용액으로 미세 균열·손상층 제거

- 목적: 표면·내부 응력 제거, 결함 감소

6️⃣ CMP 연마 (Chemical Mechanical Polishing)

- 결과: 거울처럼 매끄러운 미러 웨이퍼(Mirror Wafer)

- 정밀도

- 표면 거칠기: 수 Å(옹스트롬) 수준

- 중요성: 미세선폭 공정(7nm 이하) 필수 조건

7️⃣ 세정 · 검사 · 출하

- 세정(Cleaning): 초순수 + 화학 약품

- 검사(Inspection)

- 두께(TTV)

- 평탄도

- 파티클·결함 검사

- 출하: 팹(파운드리·IDM)으로 공급

📌 전체 공정 한눈에 정리

🎯 핵심 요약

- 웨이퍼 제조는 반도체 성능을 결정하는 가장 기초 공정

- 미세공정 시대일수록 평탄도·결함 밀도·순도가 수율을 좌우

- AI·HBM·첨단 로직 공정일수록 300mm 초고품질 웨이퍼 중요성 급증1️⃣ 원재료 정제 (고순도 실리콘 확보)

2. 전공정: 완성 웨이퍼(Completed Wafer) 제조 공정

1) 전공정 (FEOL: Front-End Of Line)

핵심 공정

- 산화(Oxidation): SiO₂ 절연막 형성

- 노광(Photo-Lithography 포토리소그래피): 회로 패턴을 빛으로 전사(EUV (Extreme Ultraviolet, 극자외선) /DUV (Deep Ultraviolet, 심자외선) )

- 식각(Etching): 불필요한 부분 제거(건식/습식)

- 이온주입(Ion Implantation): 전기적 특성 제어

- 증착(Deposition): CVD (Chemical Vapor Deposition, 화학 기상 증착) /ALD ALD (Atomic Layer Deposition, 원자층 증착) /PVD (Physical Vapor Deposition, 물리 기상 증착) 로 박막 형성

포인트: 미세화(≤7nm)에서는 EUV와 ALD의 정밀도가 성능·수율을 좌우합니다.

2) 후공정 (BEOL: Back-End Of Line)

핵심 공정

- 절연막(Low-k) 형성: 배선 간 간섭 감소

- 금속 배선(Cu, Co): 다마신(Damascene) 공정

- 다층 배선 적층: 수십~수백 개 레이어

포인트: 배선 저항·지연 최소화가 고성능의 관건

3) 웨이퍼 테스트 (Wafer Test)

- 프로브 카드로 각 칩 접촉

- 불량 다이는 잉크/맵으로 표시

2. 후공정: 패키징 & 최종 테스트

1)웨이퍼 다이싱 (Wafer Dicing / Sawing))

목적

- 웨이퍼를 개별 칩(Die) 단위로 분리

🔹 방식

| 블레이드 다이싱 | 가장 일반적 |

| 레이저 다이싱 | 미세·저손상 |

| 스텔스 다이싱 | 내부 균열 유도 |

🔹 핵심 포인트

- 칩 손상 방지

- 절단면 크랙 최소화

- 수율 직접 영향

2) 다이 접착 (Die Attach)

🔹 목적

- 분리된 칩을 패키지 기판(Substrate) 또는 리드프레임에 고정

🔹 방식

- 에폭시 접착

- 솔더 접합

- 실버 페이스트(고출력)

🔹 중요 요소

- 열 방출(방열)

- 접착 신뢰성

- 평탄도

3) 본딩 (Interconnection / Bonding)

🔹 목적

- 칩과 외부 핀을 전기적으로 연결

🔹 주요 방식

| 와이어 | 낮음 | 낮음 | ★ | 레거시 |

| 플립칩 | 중 | 중 | ★★ | CPU·GPU |

| TC 본딩 | 높음 | 높음 | ★★★ | HBM3 |

| 하이브리드 | 최상 | 최상 | ★★★★★ | HBM4+ |

| 웨이퍼 본딩 | 높음 | 높음 | ★★★★ | 3D IC |

🔹 트렌드

- AI·HBM → 플립칩 + TSV

4️⃣ 몰딩 / 캡슐화 (Encapsulation)

🔹 목적

- 칩 보호 (습기·충격·산화)

🔹 방식

- 에폭시 몰딩 컴파운드(EMC)

- 캡 몰딩 / 오픈 몰딩

🔹 핵심

- 열팽창 계수(CTE) 관리

- 패키지 워핑 방지

5️⃣ 패키지 마킹 & 절단

🔹 공정

- 레이저 마킹 (로고·정보)

- 패키지 개별 절단(Singulation)

6️⃣ 최종 테스트 (Final Test)

🔹 목적

- 실제 사용 환경에서 동작 검증

🔹 테스트 항목

- 기능 테스트

- 전기 특성

- 고온/저온

- 번인(Burn-in)

🔹 장비

- ATE (자동 테스트 장비)

📌 고급 패키징 (Advanced Packaging) – 선택

🔹 왜 필요한가?

- AI·고성능 반도체 → 대역폭·전력·열 문제

🔹 대표 기술

- 2.5D (인터포저)

- 3D 적층

- CoWoS

- HBM 패키지

📌 공정 주체

- OSAT: ASE, Amkor

- IDM: 삼성전자, 인텔

- 파운드리 연계: TSMC (CoWoS)

💡 반도체 8대 공정 핵심 체크!

글을 마치며 📝

복잡해만 보였던 반도체 공정, 알고 보니 정말 체계적이고 예술적이지 않나요? 😊 모래에서 탄생해 우리 삶의 모든 것을 제어하는 반도체의 세계는 알면 알수록 놀라운 것 같습니다. 반도체 기술에 대해 더 궁금한 점이 있다면 언제든 댓글로 소통해 주세요!

📌CPU와 트랜지스터

✅ 한 줄 요약

현대 CPU 하나에는 보통 수십억~수백억 개의 트랜지스터가 들어갑니다.

1️⃣ 세대별 CPU 트랜지스터 개수 변화

| 1971 | Intel 4004 | 약 2,300개 |

| 1993 | Pentium | 약 310만 개 |

| 2006 | Core Duo | 약 1.5억 개 |

| 2015 | Core i7 | 약 20억 개 |

| 2020 | 고성능 CPU | 100억 개 이상 |

| 2024~2025 | 최신 고성능 CPU | 300~600억 개 |

📌 이것이 바로 무어의 법칙(Moore’s Law) 이 실제로 반영된 결과입니다.

2️⃣ 실제 최신 CPU 예시 (이해용 수치)

🔹 데스크톱 / 서버급 CPU

- Intel 최신 고성능 CPU

→ 약 300~500억 개 - AMD 서버용 CPU

→ 약 400~600억 개

🔹 모바일 / SoC 계열

- Apple M 시리즈 SoC

→ 약 250~400억 개

※ 공정(3nm, 4nm), 코어 수, 캐시 크기에 따라 달라집니다.

3️⃣ “코어 하나에는 몇 개?”로 나눠 보면

예시:

- 전체 트랜지스터: 400억 개

- CPU 코어 수: 16코어

👉 단순 계산:

- 코어 1개 ≈ 수십억 개 트랜지스터

📌 단, 모든 트랜지스터가 코어에만 들어가지는 않습니다.

4️⃣ 트랜지스터는 CPU 어디에 쓰일까?

| CPU 코어 (ALU, FPU, 제어) | 30~40% |

| 캐시(L1/L2/L3) | 40~50% |

| 인터커넥트 / 메모리 컨트롤러 | 10~15% |

| I/O 및 기타 | 5~10% |

👉 캐시가 의외로 트랜지스터를 가장 많이 사용합니다.

5️⃣ 왜 이렇게 많이 필요한가?

✔ 이유 ① 병렬 처리

- 코어 증가

- 파이프라인 확장

✔ 이유 ② 성능 향상

- 분기 예측기

- Out-of-Order 실행

- 대형 레지스터 파일

✔ 이유 ③ 전력 효율

- 미세 공정

- 저전력 트랜지스터 다량 배치

6️⃣ 직관적인 비유

👉 이 스위치들이 만들어내는 것이 연산, 판단, 기억, 제어입니다.

7️⃣ 핵심 정리

📌CPU: 수억개의 트랜지스터로 만들어진 결정체

├─ 코어(Core) × N

├─ 캐시(Cache: L1 / L2 / L3)

├─ 인터커넥트(코어·캐시 연결)

├─ 메모리 컨트롤러(IMC)

├─ 클럭·전력·열 관리

└─ I/O 인터페이스

1) 코어(Core)의 구성 (CPU의 핵심)

- 명령어를 독립적으로 실행하는 최소 단위 CPU

✔ 코어 내부 구성

- 제어 장치(Control Logic): 명령 해석·제어 신호 생성

- 연산 장치

- ALU: 정수 연산

- FPU: 부동소수점 연산

- SIMD/Vector Unit: 병렬 연산

- 레지스터 파일(Register File): 초고속 임시 저장

- 파이프라인/실행 유닛: Fetch–Decode–Execute–Write Back

- L1 캐시: 명령/데이터 캐시

2) 캐시(Cache) 구조

| L1 | 코어 내부 | 가장 빠름, 매우 작음 |

| L2 | 코어별 | 중간 속도 |

| L3 | 코어 공유 | 용량 큼 |

CPU 트랜지스터의 큰 비중이 캐시에 사용됩니다.

3) 인터커넥트 & 메모리 컨트롤러

- 인터커넥트: 코어↔코어, 코어↔캐시 연결 (Ring/Mesh/NoC)

- 메모리 컨트롤러(IMC): DRAM 직접 제어 → 지연 감소·대역폭 증가

4) 클럭·전력·열 관리 블록

- 클럭 생성/분배

- 전력 관리(DVFS): 전압·주파수 동적 조절

- 열 센서/스로틀링: 안정성 확보

5) I/O 및 시스템 인터페이스

- PCIe 컨트롤러

- 인터럽트 컨트롤러

- 시스템 버스

📌트랜지스터

✅ 한 문장 정의

트랜지스터는 전기 신호를 이용해 다른 전기 신호를 제어하는 ‘반도체 스위치이자 증폭기’입니다.

또는 더 직관적으로 말하면

컴퓨터의 0과 1을 만들어내는 최소 단위 부품입니다.

1️⃣ 트랜지스터의 핵심 역할

✔ ① 스위치 역할 (디지털)

- 전류 흐름 차단 = 0

- 전류 흐름 허용 = 1

👉 컴퓨터의 모든 계산은 이 ON / OFF 조합

✔ ② 증폭 역할 (아날로그)

- 아주 작은 신호 → 큰 신호로 증폭

- 센서, 통신, 오디오 회로에서 사용

2️⃣ 왜 ‘반도체’ 트랜지스터인가

- 실리콘(Si)은

- 도체 ❌

- 절연체 ❌

- 반도체 ⭕

- 불순물(Doping)을 넣어

- N형 (전자 多)

- P형 (정공 多)

- 이 조합으로 전류를 정밀하게 제어

3️⃣ 트랜지스터의 기본 구조 (대표 2종)

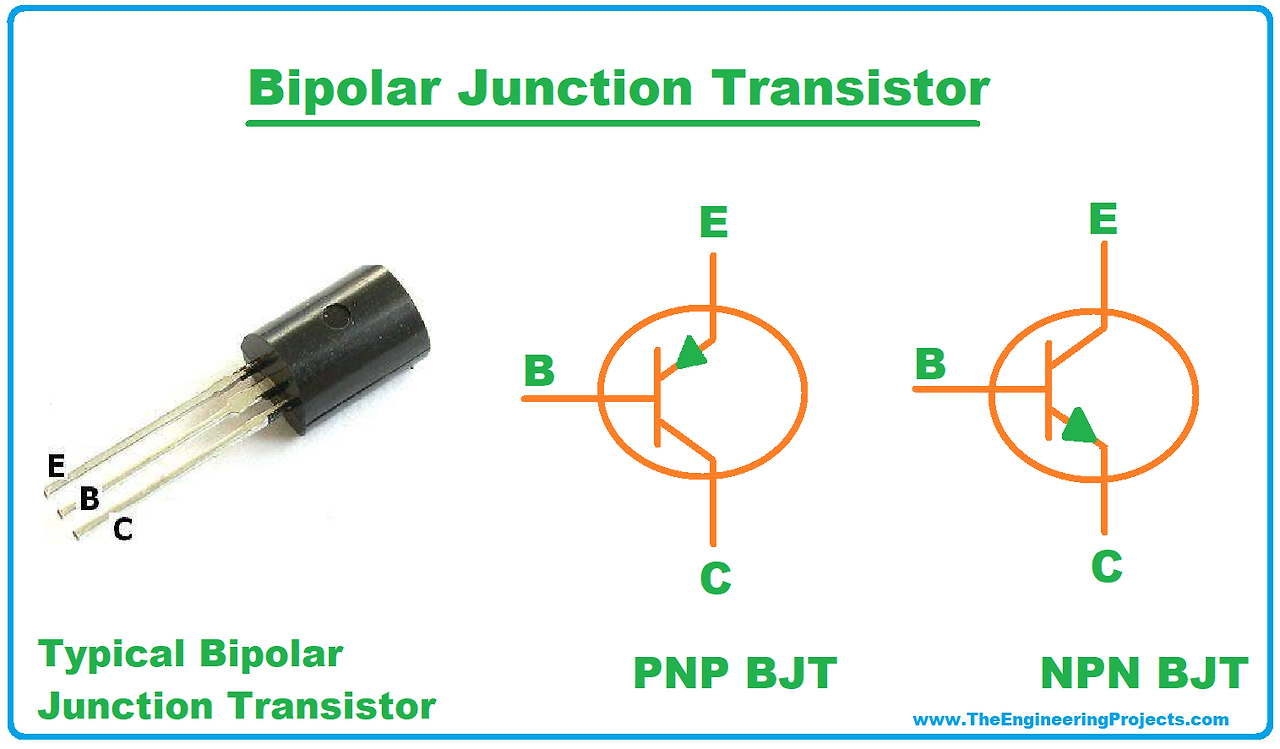

① BJT (바이폴라 접합 트랜지스터)

- 구성: Emitter / Base / Collector

- 전류로 전류를 제어

- 아날로그 증폭에 강점

② MOSFET (금속-산화막-반도체 트랜지스터)

- 구성: Gate / Source / Drain

- 전압으로 전류를 제어

- 전력 소모 적음

- 현대 CPU·메모리의 표준

📌 현재 반도체 칩의 대부분은 MOSFET

4️⃣ 트랜지스터 하나로 무엇을 할 수 있나?

- 트랜지스터 1~몇 개 → 논리 게이트

- 논리 게이트 여러 개 → 연산 회로

- 연산 회로 집합 → CPU / GPU / 메모리

5️⃣ CPU에서 트랜지스터는 무엇을 하나

CPU 내부에서 트랜지스터는:

- 덧셈·뺄셈 연산

- 비교 판단

- 데이터 저장(레지스터·캐시)

- 제어 신호 생성

- 신호 전달

👉 CPU의 모든 기능은 트랜지스터의 집합 효과

6️⃣ 트랜지스터 수와 성능의 관계

| 트랜지스터 수 ↑ | 기능·성능·캐시 증가 |

| 공정 미세화 | 더 작고 빠른 트랜지스터 |

| 설계 | 같은 수라도 성능 차이 발생 |

📌 “트랜지스터 수 = 잠재력, 설계 = 실력”

7️⃣ 직관적인 비유

8️⃣ 핵심 정리

📌반도체 설계란 무엇인가

✅ 한 문장 정의

반도체 설계란, 트랜지스터 수십억 개를 ‘어떤 기능을 하도록, 어떤 구조로, 어떤 속도·전력·면적으로’ 배치할지를 논리와 물리 규칙으로 결정하는 전 과정을 말합니다.

즉,

“칩을 어떻게 만들지”가 아니라 → “칩이 무엇을 어떻게 하게 만들지”를 정하는 일입니다.

1️⃣ 반도체 설계의 전체 그림

※ 여기서 Front-End / Back-End는

👉 제조 공정(FEOL/BEOL) 이 아니라

👉 설계 단계 구분입니다 (매우 중요).

2️⃣ ① 논리 설계 (Logic / Front-End Design)

📌 “이 칩은 무엇을 할 것인가?”

- CPU, GPU, NPU 구조 정의

- 코어 수, 캐시 크기, 연산 방식 결정

- 명령어 처리 흐름 설계

예시 질문

- 몇 코어로 할 것인가?

- 파이프라인은 몇 단계?

- 캐시는 L3까지 넣을 것인가?

- AI 연산 유닛을 넣을 것인가?

👉 칩의 ‘두뇌 구조’를 설계

2-1️⃣ RTL 설계 (Register Transfer Level)

- Verilog / VHDL 같은 HDL 언어로 회로 동작을 기술

- “이 레지스터에서 저 레지스터로 언제 데이터가 이동하는가”

📌 아직 트랜지스터는 등장하지 않음

→ 모두 논리(0과 1) 수준

2-2️⃣ 기능 검증 (Verification)

- 설계가 의도대로 동작하는지 확인

- 시뮬레이션, 테스트벤치, 에뮬레이션

👉 실제 테이프아웃 전, 버그를 잡는 가장 중요한 단계

3️⃣ ② 물리 설계 (Physical / Back-End Design)

📌 “이 논리를 실제 실리콘 위에 어떻게 올릴 것인가?”

3-1️⃣ 논리 합성 (Synthesis)

- RTL → 논리 게이트(AND, OR, NOT) 변환

- 공정 라이브러리(Standard Cell) 사용

📌 이 단계에서

- “이 논리를 만들려면 트랜지스터가 몇 개 필요한지”가 결정됨

3-2️⃣ 배치·배선 (Placement & Routing)

- 수십억 개 트랜지스터를

- 어디에 놓을지 (배치)

- 어떻게 연결할지 (배선)

👉 속도, 전력, 발열을 좌우하는 핵심 단계

3-3️⃣ 타이밍 / 전력 / 신호 무결성 검증

- 클럭이 제때 도착하는가?

- 누설 전류는 안전한가?

- 신호 간섭은 없는가?

모두 통과해야 제조 가능

4️⃣ 설계의 최종 산출물

🎯 테이프아웃 (Tape-out)

- GDSII 파일 생성

- 이 파일이 바로 파운드리로 전달됨

👉 이 순간부터는 설계 변경 불가

👉 이후는 제조 영역

5️⃣ 누가 반도체 설계를 하는가

✔ 설계 주체

- Qualcomm

- NVIDIA

- Apple

- AMD

👉 이들은 Fabless(설계 전문) 기업

✔ 제조 주체

- TSMC

- Samsung Electronics

👉 설계는 안 하거나 일부만 함, 제조 전문

6️⃣ 반도체 설계에서 결정되는 것들 (요약)

| 성능 | ⭕ |

| 전력 소모 | ⭕ |

| 발열 | ⭕ |

| 면적(원가) | ⭕ |

| 트랜지스터 수 | ⭕ |

| 공정 노드 활용도 | ⭕ |

📌 설계가 곧 제품의 80%를 결정

7️⃣ 핵심 정리

또는 한 줄로:

“반도체 설계는 수십억 개 트랜지스터에게 ‘역할과 자리’를 정해주는 일”

⚠️ 면책조항

본 내용은 참고용 초안으로, 사실과 다른 정보가 포함될 수 있습니다. 동일한 내용을 여러 증권전문가가 분석해도 각자 다른 관점과 결론을 제시하는 것처럼, 본 분석 역시 매번 해석 방식이나 강조점이 달라질 수 있습니다. 따라서, 제시된 모든 내용은 반드시 본인의 직접 검증해야 하며, 투자의 최종 결정과 책임은 사용자 본인에게 있습니다.

'투자' 카테고리의 다른 글

| 유상증자 공시 후 주가는? 반드시 체크해야 할 핵심 일자 7가지 (1) | 2026.01.04 |

|---|---|

| 하워드 막스(Howard Marks)의 이차적 사고(Second-Level Thinking) (0) | 2026.01.03 |

| 반도체 분류 (0) | 2025.12.28 |

| 심리지표 (1) | 2025.12.27 |

| 변동성 지표 (0) | 2025.12.27 |